## VIPER17

# Energy saving VIPerPlus: HV switching regulator for flyback converter

Datasheet - production data

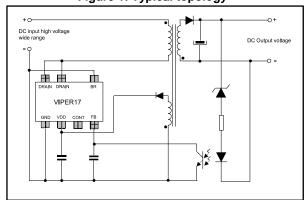

Figure 1: Typical topology

## **Features**

- 800 V avalanche rugged power section

- PWM operation with frequency jittering for low EMI

- Operating frequency:

- 60 kHz for L type

- 115 kHz for H type

- Standby power < 30 mW at 265 V<sub>AC</sub>

- Limiting current with adjustable set point

- Adjustable and accurate overvoltage protection

- On-board soft-start

- Safe auto-restart after a fault condition

- Hysteresis thermal shutdown

## **Applications**

- Adapters for PDA, camcorders, shavers, cellular phones, videogames

- Auxiliary power supply for LCD/PDP TV, monitors, audio systems, computer, industrial systems, LED driver, No el-cap LED driver

- SMPS for set-top boxes, DVD players and recorders, white goods

## **Description**

The device is an off-line converter with an 800 V rugged power section, a PWM control, two levels of overcurrent protection, overvoltage and overload protections, hysteresis thermal protection, soft-start and safe auto-restart after any fault condition removal. The burst mode operation and the device's very low consumption meet the standby energy saving regulations.

Advance frequency jittering reduces EMI filter cost. Brown-out function protects the switch mode power supply when the rectified input voltage level is below the normal minimum level specified for the system. The high voltage startup circuit is embedded in the device.

Table 1: Device summary

| 14400 201100 041111141    |             |               |  |  |  |  |

|---------------------------|-------------|---------------|--|--|--|--|

| Order code                | Package     | Packing       |  |  |  |  |

| VIPER17LN / VIPER17HN     | DIP-7       | Tube          |  |  |  |  |

| VIPER17HD / VIPER17LD     | SO16 narrow | Tube          |  |  |  |  |

| VIPER17HDTR / VIPER17LDTR |             | Tape and reel |  |  |  |  |

February 2017 DocID14419 Rev 11 1/31

## **Contents**

| 1 | Block di  | agram                                                           | 3  |

|---|-----------|-----------------------------------------------------------------|----|

| 2 | Typical   | power                                                           | 3  |

| 3 | Pin setti | ngs                                                             | 4  |

| 4 |           | al data                                                         |    |

|   | 4.1       | Maximum ratings                                                 | 5  |

|   | 4.2       | Thermal data                                                    |    |

|   | 4.3       | Electrical characteristics                                      | 6  |

| 5 | Typical ( | electrical characteristics                                      | 10 |

| 6 |           | circuit                                                         |    |

| 7 |           | on descriptions                                                 |    |

|   | 7.1       | Power section and gate driver                                   | 14 |

|   | 7.2       | High voltage startup generator                                  | 14 |

|   | 7.3       | Power-up and soft-startup                                       | 14 |

|   | 7.4       | Power down operation                                            | 17 |

|   | 7.5       | Auto restart operation                                          | 17 |

|   | 7.6       | Oscillator                                                      | 17 |

|   | 7.7       | Current mode conversion with adjustable current limit set point | 18 |

|   | 7.8       | Overvoltage protection (OVP)                                    | 18 |

|   | 7.9       | About CONT pin                                                  | 20 |

|   | 7.10      | Feed-back and overload protection (OLP)                         | 20 |

|   | 7.11      | Burst-mode operation at no load or very light load              | 23 |

|   | 7.12      | Brown-out protection                                            | 23 |

|   | 7.13      | 2nd level overcurrent protection and hiccup mode                | 25 |

| 8 | Package   | e information                                                   | 26 |

|   | 8.1       | SO16 narrow package information                                 | 26 |

|   | 8.2       | DIP-7 package information                                       | 28 |

| 9 | Revision  | n history                                                       | 30 |

VIPER17 Block diagram

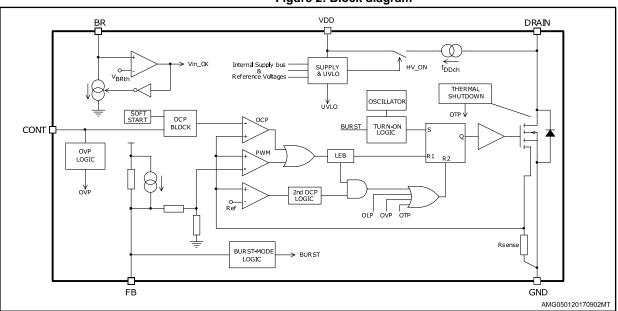

# 1 Block diagram

Figure 2: Block diagram

# 2 Typical power

Table 2: Typical power

| Dort number | 230 V <sub>AC</sub> |                | 85-265 V <sub>AC</sub> |                |  |

|-------------|---------------------|----------------|------------------------|----------------|--|

| Part number | Adapter (1)         | Open frame (2) | Adapter (1)            | Open frame (2) |  |

|             | 9 W                 | 10 W           | 5 W                    | 6 W            |  |

### Notes:

$<sup>^{(1)}</sup>$ Typical continuous power in non ventilated enclosed adapter measured at 50  $^{\circ}$ C ambient.

<sup>(2)</sup>Maximum practical continuous power in an open frame design at 50 °C ambient, with adequate heat sinking.

Pin settings VIPER17

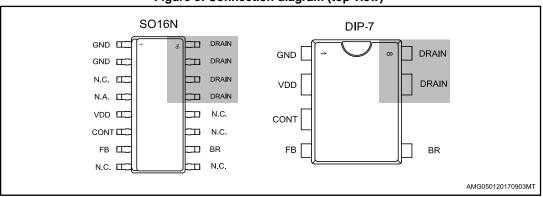

# 3 Pin settings

Figure 3: Connection diagram (top view)

The copper area for heat dissipation has to be designed under the DRAIN pins.

Table 3: Pin description

| Pir   | n.    | Name  | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-------|-------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DIP-7 | SO16  | Name  | runction                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 1     | 12    | GND   | This pin represents the device ground and the source of the power section.                                                                                                                                                                                                                                                                                                                                                                                              |

| -     | 4     | N.A.  | Not available for user. This pin is mechanically connected to the controller die pad of the frame. In order to improve the noise immunity, is highly recommended connect it to GND (pin 1-2).                                                                                                                                                                                                                                                                           |

| 2     | 5     | VDD   | Supply voltage of the control section. This pin also provides the charging current of the external capacitor during startup time.                                                                                                                                                                                                                                                                                                                                       |

| 3     | 6     | CONT  | Control pin. The following functions can be selected:  1. current limit set point adjustment. The internal set default value of the cycle-by-cycle current limit can be reduced by connecting to ground an external resistor.  2. output voltage monitoring. A voltage exceeding VovP threshold (see <i>Table 8: "Controller section"</i> ) shuts the IC down reducing the device consumption. This function is strobed and digitally filtered for high noise immunity. |

| 4     | 7     | FB    | Control input for duty cycle control. Internal current generator provides bias current for loop regulation. A voltage below the threshold V <sub>FBbm</sub> activates the burst-mode operation. A level close to the threshold V <sub>FBlin</sub> means that we are approaching the cycle-by-cycle over-current set point.                                                                                                                                              |

| 5     | 10    | BR    | Brownout protection input with hysteresis. A voltage below the threshold $V_{BRth}$ shuts down (not latch) the device and lowers the power consumption. Device operation restarts as the voltage exceeds the threshold $V_{BRth} + V_{BRhyst}$ .  It can be connected to ground when not used.                                                                                                                                                                          |

| 7,8   | 13-16 | DRAIN | High voltage drain pin. The built-in high voltage switched startup bias current is drawn from this pin too. Pins connected to the metal frame to facilitate heat dissipation.                                                                                                                                                                                                                                                                                           |

VIPER17 Electrical data

## 4 Electrical data

## 4.1 Maximum ratings

**Table 4: Absolute maximum ratings**

| Symbol               | Pin (DIP-7)                   | Parameter                                                         | ,    | Unit         |      |

|----------------------|-------------------------------|-------------------------------------------------------------------|------|--------------|------|

| Symbol               | Symbol Fill (DIF-7) Farameter |                                                                   | Min. | Max.         | Unit |

| V <sub>DRAIN</sub>   | 7, 8                          | Drain-to-source (ground) voltage                                  |      | 800          | V    |

| Eav                  | 7, 8                          | Repetitive avalanche energy (limited by T <sub>J</sub> = 150 °C)  |      | 2            | mJ   |

| I <sub>AR</sub>      | 7, 8                          | Repetitive avalanche current (limited by T <sub>J</sub> = 150 °C) |      | 1            |      |

| IDRAIN               | 7, 8                          | Pulse drain current                                               |      | 2.5          | Α    |

| Vcont                | 3                             | Control input pin voltage (with I <sub>CONT</sub> = 1 mA)         | -0.3 | Self limited | ٧    |

| V <sub>FB</sub>      | 4                             | Feed-back voltage                                                 | -0.3 | 5.5          | V    |

| V <sub>BR</sub>      | 5                             | Brown-out input pin voltage (with I <sub>BR</sub> = 0.5 mA)       | -0.3 | Self limited | V    |

| $V_{DD}$             | 2                             | Supply voltage (I <sub>DD</sub> = 25 mA)                          | -0.3 | Self limited | V    |

| I <sub>DD</sub>      | 2                             | Input current                                                     |      | 25           | mA   |

| Ртот                 |                               | Power dissipation at T <sub>A</sub> < 40 °C (DIP-7)               |      | 1            | W    |

| FIOI                 |                               | Power dissipation at T <sub>A</sub> < 60 °C (SO16N)               |      | 1            | W    |

| TJ                   |                               | Operating junction temperature range                              | -40  | 150          | °C   |

| T <sub>STG</sub>     |                               | Storage temperature                                               | -55  | 150          | °C   |

| ESD <sub>(HBM)</sub> | 1 to 8                        | Human body model                                                  |      | 4            | kV   |

| ESD(CDM)             | 1 to 8                        | Charge device model                                               |      | 1.5          | kV   |

## 4.2 Thermal data

Table 5: Thermal data

| Symbol            | Parameter                                                        | Max. value<br>SO16N | Max. value<br>DIP-7 | Unit |

|-------------------|------------------------------------------------------------------|---------------------|---------------------|------|

| R <sub>thJP</sub> | Thermal resistance junction pin (dissipated power = 1 W)         | 35                  | 40                  | °C/W |

| R <sub>thJA</sub> | Thermal resistance junction ambient (dissipated power = 1 W)     | 110                 | 110                 | °C/W |

| R <sub>thJA</sub> | Thermal resistance junction ambient (dissipated power = 1 W) (1) | 80                  | 90                  | °C/W |

### Notes:

$<sup>^{(1)}\!</sup>When$  mounted on a standard single side FR4 board with 100 mm² (0.155 sq in) of Cu (35  $\mu m$  thick).

Electrical data VIPER17

## 4.3 Electrical characteristics

$(T_J = -25 \text{ to } 125 \text{ °C}, V_{DD} = 14 \text{ V})^a$

**Table 6: Power section**

| Symbol              | Parameter                                     | Test condition                                                                              | Min. | Тур. | Max. | Unit |

|---------------------|-----------------------------------------------|---------------------------------------------------------------------------------------------|------|------|------|------|

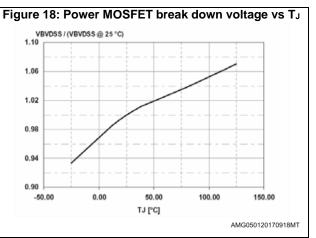

| V <sub>BVDSS</sub>  | Break-down voltage                            | $I_{DRAIN} = 1 \text{ mA}$ $V_{FB} = GND$ $T_{J} = 25 \text{ °C}$                           | 800  |      |      | ٧    |

|                     | OFF state drain current                       | V <sub>DRAIN</sub> = 640 V<br>V <sub>FB</sub> = GND                                         |      |      | 60   | μΑ   |

| loff                |                                               | V <sub>DRAIN</sub> = 800 V<br>V <sub>FB</sub> = GND                                         |      |      | 75   | μΑ   |

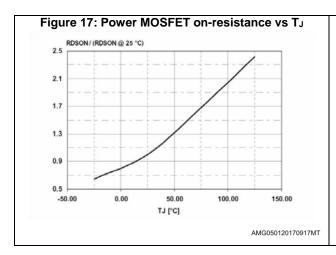

|                     |                                               | $I_{DRAIN} = 0.2 \text{ A},$ $V_{FB} = 3 \text{ V}$ $V_{BR} = GND,$ $T_{J} = 25 \text{ °C}$ |      | 20   | 24   | Ω    |

| R <sub>DS(on)</sub> | Drain-source on state resistance              | $I_{DRAIN} = 0.2 \text{ A}$ $V_{FB} = 3 \text{ V}$ $V_{BR} = GND$ $T_{J} = 125 \text{ °C}$  |      | 40   | 48   | Ω    |

| Coss                | Effective (energy related) output capacitance | V <sub>DRAIN</sub> = 0 to 640 V                                                             |      | 10   |      | pF   |

Table 7: Supply section

| Symbol                   | Parameter                                        | Test condition                                                                                        | Min. | Тур. | Max. | Unit |

|--------------------------|--------------------------------------------------|-------------------------------------------------------------------------------------------------------|------|------|------|------|

| Voltage                  |                                                  |                                                                                                       |      |      |      |      |

| V <sub>DRAIN_START</sub> | Drain-source start voltage                       |                                                                                                       | 60   | 80   | 100  | V    |

| IDDch                    | Startup charging current                         | V <sub>DRAIN</sub> = 120 V<br>V <sub>BR</sub> = GND<br>V <sub>FB</sub> = GND<br>V <sub>DD</sub> = 4 V | -2   | -3   | -4   | mA   |

|                          |                                                  | $V_{DRAIN} = 120 \text{ V}$ $V_{BR} = GND$ $V_{FB} = GND$ $V_{DD} = 4 \text{ V}$ after fault.         | -0.4 | -0.6 | -0.8 | mA   |

| $V_{DD}$                 | Operating voltage range                          | After turn-on                                                                                         | 8.5  |      | 23.5 | V    |

| V <sub>DDclamp</sub>     | V <sub>DD</sub> clamp voltage                    | I <sub>DD</sub> = 20 mA                                                                               | 23.5 |      |      | V    |

| $V_{DDon}$               | V <sub>DD</sub> startup threshold                | V <sub>DRAIN</sub> = 120 V                                                                            | 13   | 14   | 15   | V    |

| $V_{DDoff}$              | V <sub>DD</sub> under voltage shutdown threshold | V <sub>BR</sub> = GND<br>V <sub>FB</sub> = GND                                                        | 7.5  | 8    | 8.5  | V    |

| VDD(RESTART)             | V <sub>DD</sub> restart voltage threshold        | $V_{DRAIN} = 120 \text{ V}$ $V_{BR} = GND$ $V_{FB} = GND$                                             | 4    | 4.5  | 5    | V    |

$<sup>^{\</sup>rm a}$  Adjust  $V_{\rm DD}$  above  $V_{\rm DDon}$  startup threshold before settings to 14 V.

57

VIPER17 Electrical data

| Symbol              | Parameter                                                           | Test condition                                                                   | Min. | Тур. | Max. | Unit |

|---------------------|---------------------------------------------------------------------|----------------------------------------------------------------------------------|------|------|------|------|

| Current             |                                                                     |                                                                                  |      |      |      |      |

| I <sub>DD0</sub>    | Operating supply current, not switching                             | $V_{FB} = GND$ $F_{SW} = 0 \text{ kHz}$ $V_{BR} = GND$ , $V_{DD} = 10 \text{ V}$ |      |      | 0.9  | mA   |

| 1                   | Operating august augustahing                                        | V <sub>DRAIN</sub> = 120 V<br>F <sub>SW</sub> = 60 kHz                           |      |      | 1.8  | mA   |

| I <sub>DD1</sub>    | Operating supply current, switching                                 | V <sub>DRAIN</sub> = 120 V<br>F <sub>SW</sub> = 115 kHz                          |      |      | 2    | mA   |

| IDD_FAULT           | Operating supply current, with protection tripping                  |                                                                                  |      |      | 400  | μΑ   |

| I <sub>DD_OFF</sub> | Operating supply current with V <sub>DD</sub> < V <sub>DD_off</sub> | V <sub>DD</sub> = 7 V                                                            |      |      | 270  | μΑ   |

### Table 8: Controller section

| Symbol               | Parameter                            | Test condition                                                                | Min. | Тур. | Max. | Unit |

|----------------------|--------------------------------------|-------------------------------------------------------------------------------|------|------|------|------|

| Feed-back p          | oin                                  |                                                                               |      |      |      |      |

| $V_{FBolp}$          | Overload shut down threshold         |                                                                               | 4.5  | 4.8  | 5.2  | V    |

| $V_{FBlin}$          | Linear dynamics upper limit          |                                                                               | 3.2  | 3.3  | 3.4  | V    |

| $V_{FBbm}$           | Burst mode threshold                 | Voltage falling                                                               | 0.4  | 0.45 | 0.6  | V    |

| V <sub>FBbmhys</sub> | Burst mode hysteresis                | Voltage rising                                                                |      | 50   |      | mV   |

|                      | Food book occurred comment           | V <sub>FB</sub> = 0.3 V                                                       | -150 | -200 | -280 | uA   |

| I <sub>FB</sub>      | Feed-back sourced current            | 3.3 V < V <sub>FB</sub> < 4.8 V                                               |      | -3   |      | uA   |

| R <sub>FB(DYN)</sub> | Dynamic resistance                   | V <sub>FB</sub> < 3.3 V                                                       | 12   |      | 19   | kΩ   |

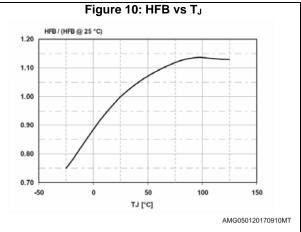

| H <sub>FB</sub>      | ΔV <sub>FB</sub> / ΔI <sub>D</sub>   |                                                                               | 3    |      | 8    | V/A  |

| CONT pin             |                                      |                                                                               |      |      |      | •    |

| VCONT_I              | Low level clamp voltage              | I <sub>CONT</sub> = -100 μA                                                   |      | 0.5  |      | V    |

| VCONT_h              | High level clamp voltage             | Icont = 1 mA                                                                  | 5    | 5.5  | 6    | V    |

| Current limi         | tation                               |                                                                               |      |      |      | •    |

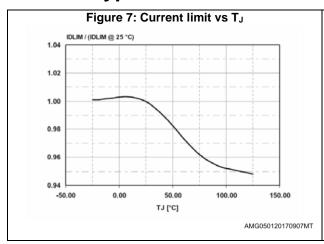

| l <sub>Dlim</sub>    | Max drain current limitation (1)     | V <sub>FB</sub> = 4 V<br>I <sub>CONT</sub> = -10 μA<br>T <sub>J</sub> = 25 °C | 0.38 | 0.4  | 0.42 | А    |

| tss                  | Soft-start time                      |                                                                               |      | 8.5  |      | ms   |

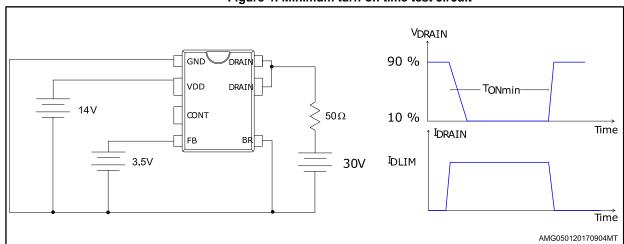

| Ton_min              | Minimum turn ON time                 |                                                                               | 220  | 400  | 480  | ns   |

| td                   | Propagation delay                    | (2)                                                                           |      | 100  |      | ns   |

| t <sub>LEB</sub>     | Leading edge blanking                | (2)                                                                           |      | 300  |      | ns   |

| I <sub>D_BM</sub>    | Peak drain current during burst mode | V <sub>FB</sub> = 0.6 V                                                       |      | 90   |      | mA   |

Electrical data VIPER17

| Symbol               | Parameter                                  | Test condition                            | Min. | Тур. | Max. | Unit |

|----------------------|--------------------------------------------|-------------------------------------------|------|------|------|------|

| Oscillator s         | ection                                     |                                           |      |      |      |      |

|                      | VIPER17L                                   | V <sub>DD</sub> = operating voltage range | 54   | 60   | 66   | kHz  |

| Fosc                 | VIPER17H                                   | V <sub>FB</sub> = 1 V                     | 103  | 115  | 127  | kHz  |

| רם                   | Madulation donth                           | VIPER17L                                  |      | ±4   |      | kHz  |

| FD                   | Modulation depth                           | VIPER17H                                  |      | ±8   |      | kHz  |

| FM                   | Modulation frequency                       |                                           |      | 250  |      | Hz   |

| D <sub>MAX</sub>     | Maximum duty cycle                         |                                           | 70   |      | 80   | %    |

| Overcurren           | t protection (2 <sup>nd</sup> OCP)         |                                           |      |      |      |      |

| I <sub>DMAX</sub>    | Second over current threshold              | (2)                                       |      | 0.6  |      | Α    |

| Overvoltage          | e protection                               |                                           |      |      |      |      |

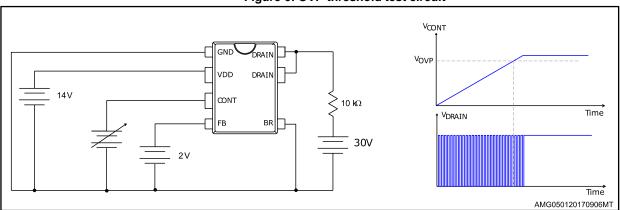

| Vovp                 | Overvoltage protection threshold           |                                           | 2.7  | 3    | 3.3  | V    |

| TSTROBE              | Overvoltage protection strobe time         |                                           |      | 2.2  |      | μs   |

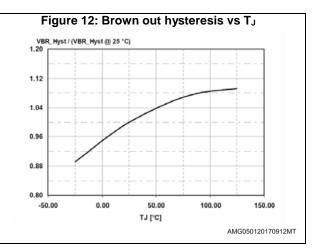

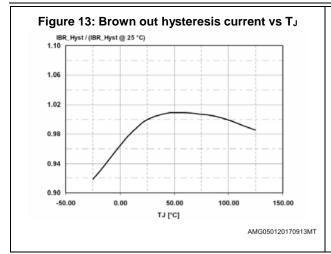

| Brown out            | protection                                 |                                           |      |      |      |      |

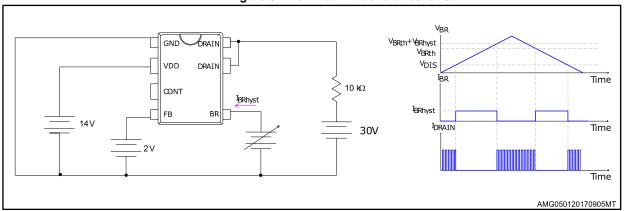

| $V_{BRth}$           | Brown out threshold                        | Voltage falling                           | 0.41 | 0.45 | 0.49 | V    |

| V <sub>BRhyst</sub>  | Voltage hysteresis above V <sub>BRth</sub> |                                           |      | 50   |      | mV   |

| I <sub>BRhyst</sub>  | Current hysteresis                         |                                           | 7    |      | 12   | μA   |

| V <sub>BRclamp</sub> | Clamp voltage                              | I <sub>BR</sub> = 250 μA                  |      | 3    |      | V    |

| V <sub>DIS</sub>     | Brown out disable voltage                  |                                           | 50   |      | 150  | mV   |

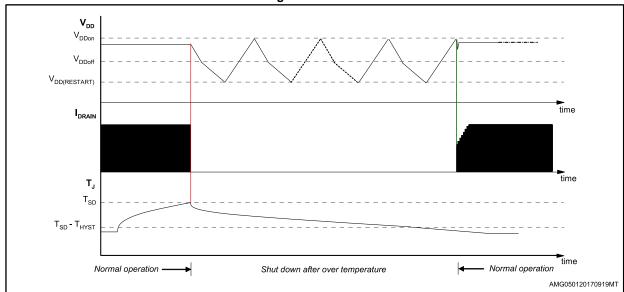

| Thermal sh           | Thermal shutdown                           |                                           |      |      |      |      |

| T <sub>SD</sub>      | Thermal shutdown temperature               | (2)                                       | 150  | 160  |      | °C   |

| T <sub>HYST</sub>    | Thermal shutdown hysteresis                | (2)                                       |      | 30   |      | °C   |

### Notes:

$<sup>^{(1)}</sup>I_{Dlim}$  @  $V_{DD}$  lower than 10 V can range between -5 % and +15 %.

$<sup>^{(2)}</sup>$ Specification assured by design, characterization and statistical correlation.

VIPER17 Electrical data

Figure 4: Minimum turn-on time test circuit

Figure 5: Brown out threshold test circuit

Figure 6: OVP threshold test circuit

Adjust  $V_{DD}$  above  $V_{DDon}$  startup threshold before settings to 14 V.

# 5 Typical electrical characteristics

Figure 14: Operating supply current (no switching) vs T<sub>J</sub> IDD0 / (IDD0 @ 25 °C) 1.06 1.04 1.01 0.99 0.96 0.94 50.00 -50.00 0.00 100.00 150.00 TJ [°C] AMG050120170914MT

Figure 15: Operating supply current (switching) vs TJ

1.06

1.04

1.01

0.99

0.96

0.94

-50.00

0.00

50.00

100.00

150.00

AMG050120170915MT

Figure 19: Thermal shutdown

VIPER17 Typical circuit

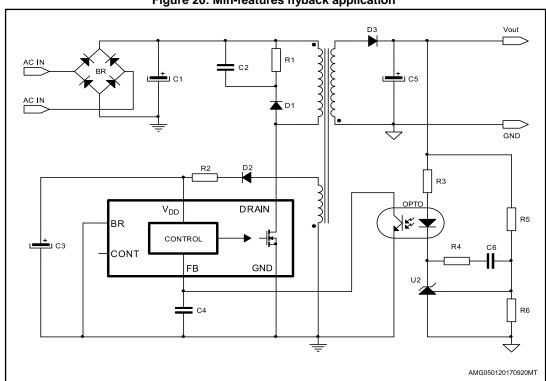

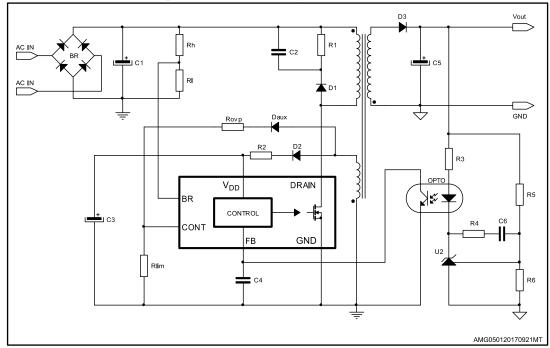

# 6 Typical circuit

Figure 20: Min-features flyback application

Figure 21: Full-features flyback application

## 7 Operation descriptions

VIPER17 is a high-performance low-voltage PWM controller chip with an 800 V, avalanche rugged power section.

The controller includes: the oscillator with jittering feature, the startup circuits with soft-start feature, the PWM logic, the current limit circuit with adjustable set point, the second over current circuit, the burst mode management, the brown-out circuit, the UVLO circuit, the auto-restart circuit and the thermal protection circuit.

The current limit set-point is set by the CONT pin. The burst mode operation guaranties high performance in the stand-by mode and helps in the energy saving norm accomplishment.

All the fault protections are built in auto restart mode with very low repetition rate to prevent IC's over heating.

## 7.1 Power section and gate driver

The power section is implemented with an avalanche ruggedness N-channel MOSFET, which guarantees safe operation within the specified energy rating as well as high dv/dt capability. The power section has a BV<sub>DSS</sub> of 800 V min. and a typical R<sub>DS(on)</sub> of 20  $\Omega$  at 25 °C.

The integrated SenseFET structure allows a virtually loss-less current sensing.

The gate driver is designed to supply a controlled gate current during both turn-on and turn-off in order to minimize common mode EMI. Under UVLO conditions an internal pull-down circuit holds the gate low in order to ensure that the Power section cannot be turned on accidentally.

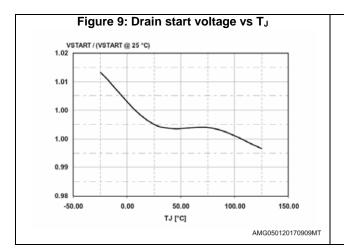

## 7.2 High voltage startup generator

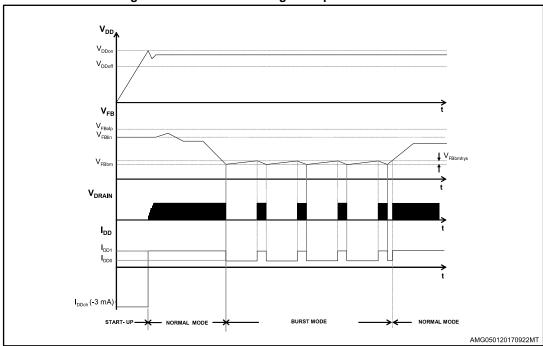

The HV current generator is supplied through the DRAIN pin and it is enabled only if the input bulk capacitor voltage is higher than  $V_{DRAIN\_START}$  threshold, 80  $V_{DC}$  typically. When the HV current generator is ON, the  $I_{DDch}$  current (3 mA typical value) is delivered to the capacitor on the  $V_{DD}$  pin. In case of auto restart mode after a fault event, the  $I_{DDch}$  current is reduced to 0.6 mA, in order to have a slow duty cycle during the restart phase.

## 7.3 Power-up and soft-startup

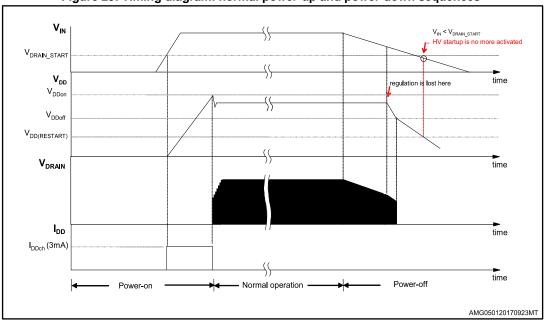

If the input voltage rises up till the device start threshold, V<sub>DRAIN\_START</sub>, the V<sub>DD</sub> voltage begins to grow due to the I<sub>DDch</sub> current (see *Table 7: "Supply section "*) coming from the internal high voltage startup circuit. If the V<sub>DD</sub> voltage reaches V<sub>DDon</sub> threshold (see *Table 7: "Supply section"*) the power MOSFET starts switching and the HV current generator is turned OFF. See *Figure 23: "Timing diagram: normal power-up and power-down sequences"*.

The IC is powered by the energy stored in the capacitor on the VDD pin,  $C_{VDD}$ , until when the self-supply circuit (typically an auxiliary winding of the transformer and a steering diode) develops a voltage high enough to sustain the operation.

$C_{VDD}$  capacitor must be sized enough to avoid fast discharge and keep the needed voltage value higher than  $V_{DDoff}$  threshold. In fact, a too low capacitance value could terminate the switching operation before the controller receives any energy from the auxiliary winding.

The following formula can be used for the V<sub>DD</sub> capacitor calculation:

### **Equation 1**

$$C_{VDD} = \frac{I_{DDch} \times t_{SSaux}}{V_{DDon} - V_{DDoff}}$$

The  $t_{SSaux}$  is the time needed for the steady state of the auxiliary voltage. This time is estimated by applicator according to the output stage configurations (transformer, output capacitances, etc.).

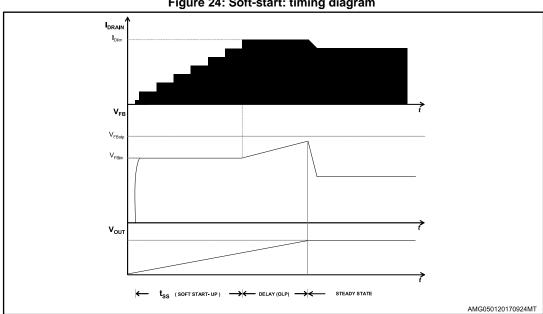

During the converter startup time, the drain current limitation is progressively increased to the maximum value. In this way the stress on the secondary diode is considerably reduced. It also helps to prevent transformer saturation. The soft-start time lasts 8.5 ms and the feature is implemented for every attempt of startup converter or after a fault.

Figure 22: IDD current during startup and burst mode

Figure 23: Timing diagram: normal power-up and power-down sequences

Figure 24: Soft-start: timing diagram

## 7.4 Power down operation

At converter power down, the system loses regulation as soon as the input voltage is so low that the peak current limitation is reached. The V<sub>DD</sub> voltage drops and when it falls below the V<sub>DDoff</sub> threshold (see *Table 7: "Supply section"*) the power MOSFET is switched OFF, the energy transfers to the IC interrupted and consequently the V<sub>DD</sub> voltages decreases, *Figure 23: "Timing diagram: normal power-up and power-down sequences"*. Later, if the V<sub>IN</sub> is lower than V<sub>DRAIN\_START</sub> (see *Table 7: "Supply section"*), the startup sequence is inhibited and the power down completed. This feature is useful to prevent converter's restart attempts and ensures monotonic output voltage decay during the system power down.

## 7.5 Auto restart operation

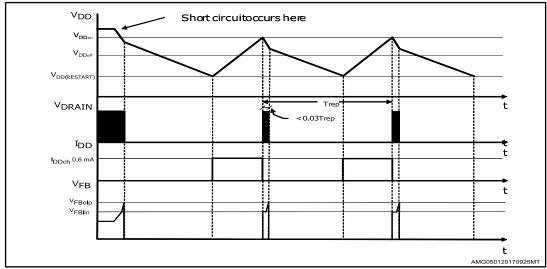

If after a converter power down, the  $V_{IN}$  is higher than  $V_{DRAIN\_START}$ , the startup sequence is not inhibited and will be activated only when the  $V_{DD}$  voltage drops down the  $V_{DD(RESTART)}$  threshold (see *Table 7: "Supply section"*). This means that the HV startup current generator restarts the  $V_{DD}$  capacitor charging only when the  $V_{DD}$  voltage drops below  $V_{DD(RESTART)}$ . The scenario above described is for instance a power down because of a fault condition. After a fault condition, the charging current,  $I_{DDch}$ , is 0.6 mA (typ.) instead of the 3 mA (typ.) of a normal startup converter phase. This feature together with the low  $V_{DD(RESTART)}$  threshold ensures that, after a fault, the restart attempts of the IC has a very long repetition rate and the converter works safely with extremely low power throughput. The *Figure 25: "Timing diagram: behavior after short circuit"* shows the IC behavioral after a short circuit event.

Figure 25: Timing diagram: behavior after short circuit

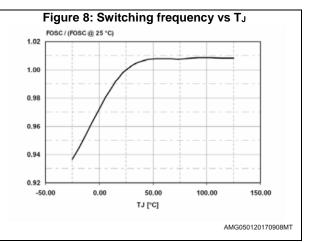

### 7.6 Oscillator

The switching frequency is internally fixed to 60 kHz or 115 kHz. In both case the switching frequency is modulated by approximately ±4 kHz (60 kHz version) or ±8 kHz (115 kHz version) at 250 Hz (typical) rate, so that the resulting spread-spectrum action distributes the energy of each harmonic of the switching frequency over a number of side-band harmonics having the same energy on the whole but smaller amplitudes.

# 7.7 Current mode conversion with adjustable current limit set point

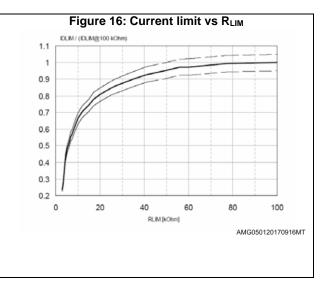

The device is a current mode converter: the drain current is sensed and converted in voltage that is applied to the non inverting pin of the PWM comparator. This voltage is compared with the one on the feed-back pin through a voltage divider on cycle by cycle basis. The VIPER17 has a default current limit value, IDLIM, that the designer can adjust according the electrical specification, by the RLIM resistor connected to the CONT see Figure 16: "Current limit vs RLIM".

The CONT pin has a minimum current sunk needed to activate the  $I_{DLIM}$  adjustment: without  $R_{LIM}$  or with high  $R_{LIM}$  (i.e. 100 K $\Omega$ ) the current limit is fixed to the default value (see  $I_{DLIM}$ , Table 8: "Controller section").

## 7.8 Overvoltage protection (OVP)

The VIPER17has integrated the logic for the monitor of the output voltage using as input signal the voltage  $V_{\text{CONT}}$  during the OFF time of the power MOSFET. This is the time when the voltage from the auxiliary winding tracks the output voltage, through the turn ratio

$\frac{N_{AUX}}{N_{SEC}}$

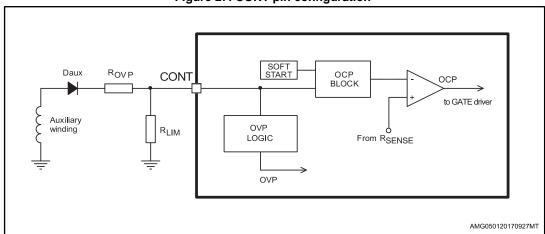

The CONT pin has to be connected to the auxiliary winding through the diode  $D_{OVP}$  and the resistors  $R_{OVP}$  and  $R_{LIM}$  as shows the *Figure 27: "CONT pin configuration"*. When, during the OFF time, the voltage  $V_{CONT}$  exceeds, four consecutive times, the reference voltage  $V_{OVP}$  (see *Table 8: "Controller section"*) the overvoltage protection will stop the power MOSFET and the converter enters the auto-restart mode.

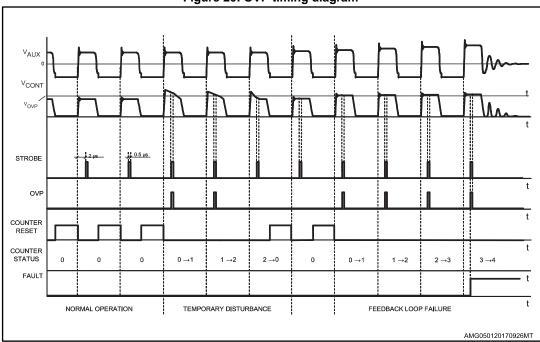

In order to bypass the noise immediately after the turn off of the power MOSFET, the voltage V<sub>CONT</sub> is sampled inside a short window after the time T<sub>STROBE</sub>, see *Table 8:* "Controller section" and the *Figure 26:* "OVP timing diagram". The sampled signal, if higher than V<sub>OVP</sub>, trigger the internal OVP digital signal and increments the internal counter. The same counter is reset every time the signal OVP is not triggered in one oscillator cycle.

Referring to the *Figure 21: "Full-features flyback application"*, the resistors divider ratio k<sub>OVP</sub> will be given by:

### **Equation 2**

$$K_{OVP} = \frac{V_{OVP}}{\frac{N_{AUX}}{N_{SEC}} \cdot (V_{OUTOVP} + V_{DSEC}) - V_{DAUX}}$$

### **Equation 3**

$$K_{OVP} = \frac{R_{LIM}}{R_{LIM} + R_{OVP}}$$

### Where:

- Vove is the OVP threshold (see *Table 8: "Controller section"*)

- V<sub>OUT OVP</sub> is the converter output voltage value to activate the OVP (set by designer)

- N<sub>AUX</sub> is the auxiliary winding turns

- N<sub>SEC</sub> is the secondary winding turns

- V<sub>DSEC</sub> is the secondary diode forward voltage

- V<sub>DAUX</sub> is the auxiliary diode forward voltage

- ROVP together RLIM make the output voltage divider

Than, fixed R<sub>LIM</sub>, according to the desired I<sub>DLIM</sub>, the R<sub>OVP</sub> can be calculating by:

### **Equation 4**

$$R_{OVP} = R_{LIM} \times \frac{1 - K_{OVP}}{K_{OVP}}$$

The resistor values will be such that the current sourced and sunk by the CONT pin be within the rated capability of the internal clamp.

Figure 26: OVP timing diagram

#### 7.9 About CONT pin

Referring to the Figure 27: "CONT pin configuration", through the CONT pin, the below features can be implemented:

- 1. Current Limit set point

- 2. Over voltage protection on the converter output voltage

The Table 9: "CONT pin configurations" referring to the Figure 27: "CONT pin configuration", lists the external components needed to activate one or plus of the CONT pin functions.

Figure 27: CONT pin configuration

Table 9: CONT pin configurations

| Function / component              | R <sub>LIM</sub> (1)                   | Rove           | D <sub>AUX</sub> |

|-----------------------------------|----------------------------------------|----------------|------------------|

| I <sub>Dlim</sub> reduction       | See Figure 16: "Current limit vs RLIM" | No             | No               |

| OVP                               | ≥ 80 KΩ                                | See Equation 4 | Yes              |

| I <sub>Dlim</sub> reduction + OVP | See Figure 16: "Current limit vs RLIM" | See Equation 4 | Yes              |

### Notes:

#### Feed-back and overload protection (OLP) 7.10

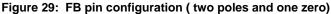

The VIPER17 is a current mode converter: the feedback pin controls the PWM operation, controls the burst mode and actives the overload protection. Figure 28: "FB pin configuration (minimal) "and Figure 29: "FB pin configuration (two poles and one zero)" show the internal current mode structure.

With the feedback pin voltage between V<sub>FBbm</sub> and V<sub>FBlin</sub>, see *Table 8: "Controller section"*, the drain current is sensed and converted in voltage that is applied to the non inverting pin of the PWM comparator. See Figure 2: "Block diagram".

This voltage is compared with the one on the feedback pin through a voltage divider on cycle by cycle basis. When these two voltages are equal, the PWM logic orders the switch off of the power MOSFET. The drain current is always limited to IDlim value.

20/31 DocID14419 Rev 11

<sup>&</sup>lt;sup>(1)</sup>R<sub>LIM</sub> has to be fixed before of R<sub>OVP</sub>.

In case of overload the feedback pin increases in reaction to this event and when it goes higher than V<sub>FBlin</sub>, the PWM comparator is disabled and the drain current is limited to I<sub>Dlim</sub> by the OCP comparator, see *Figure 2: "Block diagram"*.

When the feedback pin voltage reaches the threshold  $V_{FBlin}$  an internal current generator starts to charge the feedback capacitor ( $C_{FB}$ ) and when the feedback voltage reaches the  $V_{FBolp}$  threshold, the converter is turned off and the startup phase is activated with reduced value of  $I_{DDch}$  to 0.6 mA. See *Table 7: "Supply section"*.

During the first startup phase of the converter, after the soft-startup time, t<sub>SS</sub>, the output voltage could force the feedback pin voltage to rise up to the V<sub>FBolp</sub> threshold that switches off the converter itself.

To avoid this event, the appropriate feedback network has to be selected according to the output load. More the network feedback fixes the compensation loop stability. The *Figure 28: "FB pin configuration (minimal)"* and *Figure 29: "FB pin configuration (two poles and one zero)"* show the two different feedback networks.

The time from the over load detection ( $V_{FB} = V_{FBlin}$ ) to the device shutdown ( $V_{FB} = V_{FBolp}$ ) can be calculating by  $C_{FB}$  value (see *Figure 28: "FB pin configuration (minimal)"* and *Figure 29: "FB pin configuration (two poles and one zero)"*), using the formula:

### **Equation 5**

$$T_{OLP} - delay = C_{FB} \times \frac{V_{FBolp} - V_{FBlin}}{3\mu A}$$

In the *Figure 28: "FB pin configuration (minimal)"*, the capacitor connected to FB pin (C<sub>FB</sub>) is used as part of the circuit to compensate the feedback loop but also as element to delay the OLP shut down owing to the time needed to charge the capacitor (see *Equation 5*).

After the startup time,  $t_{SS}$ , during which the feedback voltage is fixed at  $V_{FBlin}$ , the output capacitor could not be at its nominal value and the controller interpreter this situation as an over load condition. In this case, the OLP delay helps to avoid an incorrect device shut down during the startup.

Owing to the above considerations, the OLP delay time must be long enough to by-pass the initial output voltage transient and check the over load condition only when the output voltage is in steady state. The output transient time depends from the value of the output capacitor and from the load.

When the value of the C<sub>FB</sub> capacitor calculated for the loop stability is too low and cannot ensure enough OLP delay, an alternative compensation network can be used and it is showed in *Figure 29: "FB pin configuration ( two poles and one zero)"*.

Using this alternative compensation network, two poles (f<sub>PFB</sub>, f<sub>PFB1</sub>) and one zero (f<sub>ZFB</sub>) are introduced by the capacitors C<sub>FB</sub> and C<sub>FB1</sub> and the resistor R<sub>FB1</sub>.

The capacitor C<sub>FB</sub> introduces a pole (f<sub>PFB</sub>) at higher frequency than f<sub>ZB</sub> and f<sub>PFB1</sub>. This pole is usually used to compensate the high frequency zero due to the ESR (Equivalent Series Resistor) of the output capacitance of the fly-back converter.

The mathematical expressions of these poles and zero frequency, considering the scheme in *Figure 29: "FB pin configuration ( two poles and one zero)"* are reported by the equations below:

### **Equation 6**

$$f_{ZFB} = \frac{1}{2 \cdot \pi \cdot C_{FB1} \cdot R_{FB1}}$$

**Equation 7**

$$f_{PFB1} = \frac{R_{FB(DYN)} + R_{FB1}}{2 \cdot \pi \cdot C_{FB} \cdot \left(R_{FB(DYN)} \cdot R_{FB1}\right)}$$

**Equation 8**

$$f_{PFB1} = \frac{1}{2 \cdot \pi \cdot C_{FB1} \cdot (R_{FB1} + R_{FB(DYN)})}$$

The RFB(DYN) is the dynamic resistance seen by the FB pin.

The C<sub>FB1</sub> capacitor fixes the OLP delay and usually C<sub>FB1</sub> results much higher than C<sub>FB</sub>. The Equation 5 can be still used to calculate the OLP delay time but CFB1 has to be considered instead of CFB. Using the alternative compensation network, the designer can satisfy, in all case, the loop stability and the enough OLP delay time alike.

From sense FET To PWM Logic CONTROL BURST BURST-MODE BURST-MODE LOGIC To disable logic AMG050120170928MT

Figure 28: FB pin configuration (minimal)

477

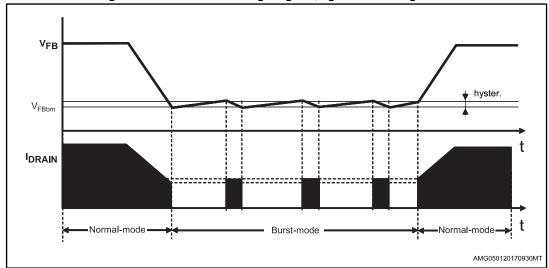

## 7.11 Burst-mode operation at no load or very light load

When the load decrease the feedback loop reacts lowering the feedback pin voltage. If it falls down the burst mode threshold, V<sub>FBbm</sub>, the power MOSFET is not more allowed to be switched on. After the MOSFET stops, as a result of the feedback reaction to the energy delivery stop, the feedback pin voltage increases and exceeding the level, V<sub>FBbm</sub> + V<sub>FBbmhys</sub>, the power MOSFET starts switching again. The burst mode thresholds are reported on *Table 8: "Controller section"* and *Figure 30: "Burst mode timing diagram, light load management"* shows this behavior. Systems alternates period of time where power MOSFET is switching to period of time where power MOSFET is not switching; this device working mode is the burst mode. The power delivered to output during switching periods exceeds the load power demands; the excess of power is balanced from not switching period where no power is processed. The advantage of burst mode operation is an average switching frequency much lower then the normal operation working frequency, up to some hundred of hertz, minimizing all frequency related losses. During the burst-mode the drain current peak is clamped to the level, I<sub>D\_BM</sub>, reported on *Table 8: "Controller section"*.

Figure 30: Burst mode timing diagram, light load management

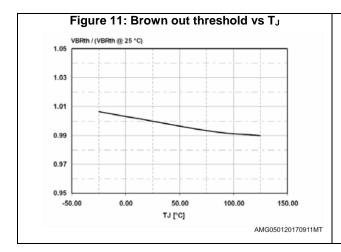

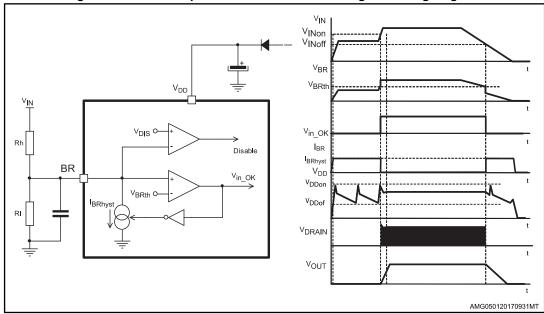

## 7.12 Brown-out protection

Brown-out protection is a not-latched shutdown function activated when a condition of mains under voltage is detected. The Brown-out comparator is internally referenced to V<sub>BRth</sub> threshold, see *Table 8: "Controller section"*, and disables the PWM if the voltage applied at the BR pin is below this internal reference. Under this condition the power MOSFET is turned off. Until the Brown out condition is present, the V<sub>DD</sub> voltage continuously oscillates between the V<sub>DDn</sub> and the UVLO thresholds, as shown in the timing diagram of *Figure 31: "Brown-out protection: BR external setting and timing diagram"*. A voltage hysteresis is present to improve the noise immunity.

The switching operation is restarted as the voltage on the pin is above the reference plus the before said voltage hysteresis. See *Figure 5: "Brown out threshold test circuit"*.

The Brown-out comparator is provided also with a current hysteresis,  $I_{BRhyst}$ . The designer has to set the rectified input voltage above which the power MOSFET starts switching after brown out event,  $V_{INon}$ , and the rectified input voltage below which the power MOSFET is switched off,  $V_{INoff}$ . Thanks to the  $I_{BRhyst}$ , see *Table 8: "Controller section"*, these two thresholds can be set separately.

Figure 31: Brown-out protection: BR external setting and timing diagram

Fixed the  $V_{INon}$  and the  $V_{INoff}$  levels, with reference to *Figure 31: "Brown-out protection: BR external setting and timing diagram"*, the following relationships can be established for the calculation of the resistors  $R_H$  and  $R_L$ :

### **Equation 9**

$$R_L = \frac{V_{BRhyst}}{I_{BRhyst}} + \frac{V_{INon} - V_{INoff} - V_{BRhyst}}{V_{INoff} - V_{BRth}} \times \frac{V_{BRth}}{I_{BRhyst}}$$

### **Equation 10**

$$R_{H} = \frac{V_{INon} - V_{INoff} - V_{BRhyst}}{I_{BRhyst}} \times \frac{R_{L}}{R_{L} + \frac{V_{BRhyst}}{I_{BPhyst}}}$$

For a proper operation of this function,  $V_{\text{IN on}}$  must be less than the peak voltage at minimum mains and  $V_{\text{IN off}}$  less than the minimum voltage on the input bulk capacitor at minimum mains and maximum load.

The BR pin is a high impedance input connected to high value resistors, thus it is prone to pick up noise, which might alter the OFF threshold when the converter operates or gives origin to undesired switch-off of the device during ESD tests.

It is possible to bypass the pin to ground with a small film capacitor (e.g. 1-10 nF) to prevent any malfunctioning of this kind.

If the brown-out function is not used the BR pin has to be connected to GND, ensuring that the voltage is lower than the minimum of  $V_{DIS}$  threshold (50 mV, see *Table 8: "Controller section"*). In order to enable the brown-out function the BR pin voltage has to be higher than the maximum of  $V_{DIS}$  threshold (150 mV, see *Table 8: "Controller section"*).

## 7.13 2nd level overcurrent protection and hiccup mode

The VIPER17 is protected against short circuit of the secondary rectifier, short circuit on the secondary winding or a hard-saturation of fly-back transformer. Such as anomalous condition is invoked when the drain current exceed the threshold I<sub>DMAX</sub> (see *Table 8: "Controller section"*).

To distinguish a real malfunction from a disturbance (e.g. induced during ESD tests) a "warning state" is entered after the first signal trip. If in the subsequent switching cycle the signal is not tripped, a temporary disturbance is assumed and the protection logic will be reset in its idle state; otherwise if the I<sub>DMAX</sub> threshold is exceeded for two consecutive switching cycles a real malfunction is assumed and the power MOSFET is turned OFF.

The shutdown condition is latched as long as the device is supplied. While it is disabled, no energy is transferred from the auxiliary winding; hence the voltage on the  $V_{DD}$  capacitor decays till the  $V_{DD}$  under voltage threshold ( $V_{DDoff}$ ), which clears the latch.

The startup HV current generator is still off, until  $V_{DD}$  voltage goes below its restart voltage,  $V_{DD(RESTART)}$ . After this condition the  $V_{DD}$  capacitor is charged again by 600  $\mu$ A current, and the converter switching restarts if the  $V_{DDon}$  occurs. If the fault condition is not removed the device enters in auto-restart mode. This behavioral results in a low-frequency intermittent operation (Hiccup-mode operation), with very low stress on the power circuit. See the timing diagram of *Figure 32: "Hiccup-mode OCP: timing diagram"*.

Figure 32: Hiccup-mode OCP: timing diagram

Package information VIPER17

## 8 Package information

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK® packages, depending on their level of environmental compliance. ECOPACK® specifications, grade definitions and product status are available at: **www.st.com**. ECOPACK® is an ST trademark.

## 8.1 SO16 narrow package information

Figure 33: SO16 narrow package outline SEATING PLANE Ε Α2 E1 Α1 200 9 ===

Table 10: SO16 narrow mechanical data

| Dim. | mm   |      |      |  |

|------|------|------|------|--|

|      | Min. | Тур. | Max. |  |

| А    |      |      | 1.75 |  |

| A1   | 0.1  |      | 0.25 |  |

| A2   | 1.25 |      |      |  |

| b    | 0.31 |      | 0.51 |  |

| С    | 0.17 |      | 0.25 |  |

| D    | 9.8  | 9.9  | 10   |  |

| Е    | 5.8  | 6    | 6.2  |  |

| E1   | 3.8  | 3.9  | 4    |  |

| е    |      | 1.27 |      |  |

| h    | 0.25 |      | 0.5  |  |

| L    | 0.4  |      | 1.27 |  |

| k    | 0    |      | 8    |  |

| ccc  |      |      | 0.1  |  |

Package information VIPER17

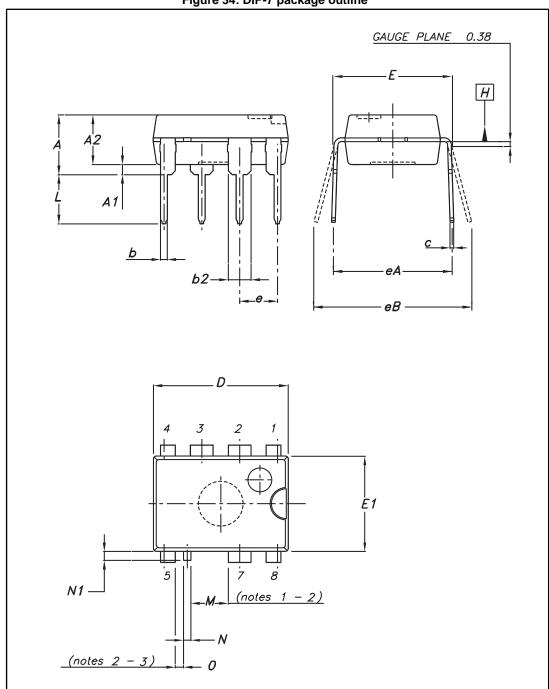

# 8.2 DIP-7 package information

Figure 34: DIP-7 package outline

Table 11: DIP-7 package mechanical data

| Dim.                | mm   |       |       | Notes |

|---------------------|------|-------|-------|-------|

|                     | Min. | Тур.  | Max.  | Notes |

| Α                   |      |       | 5.33  |       |

| A1                  | 0.38 |       |       |       |

| A2                  | 2.92 | 3.30  | 4.95  |       |

| b                   | 0.36 | 0.46  | 0.56  |       |

| b2                  | 1.14 | 1.52  | 1.78  |       |

| С                   | 0.20 | 0.25  | 0.36  |       |

| D                   | 9.02 | 9.27  | 10.16 |       |

| E                   | 7.62 | 7.87  | 8.26  |       |

| E1                  | 6.10 | 6.35  | 7.11  |       |

| е                   |      | 2.54  |       |       |

| eA                  |      | 7.62  |       |       |

| eB                  |      |       | 10.92 |       |

| L                   | 2.92 | 3.30  | 3.81  |       |

| M <sup>(1)(2)</sup> |      | 2.508 |       | 6 - 8 |

| N                   | 0.40 | 0.50  | 0.60  |       |

| N1                  |      |       | 0.60  |       |

| O <sup>(2)(3)</sup> |      | 0.548 |       | 7 - 8 |

### Notes:

### General package performance

- The leads size is comprehensive of the thickness of the leads finishing material.

- Dimensions do not include mold protrusion, not to exceed 0,25 mm in total (both side).

- Package outline exclusive of metal burrs dimensions.

- Datum plane "H" coincident with the bottom of lead, where lead exits body.

- Ref. POA MOTHER doc. 0037880.

<sup>&</sup>lt;sup>(1)</sup> Creepage distance > 800 V.

$<sup>^{\</sup>rm (2)}$  Creepage distance as shown in the 664-1 CEI / IEC standard.

<sup>(3)</sup> Creepage distance 250 V.

Revision history VIPER17

# 9 Revision history

Table 12: Document revision history

| Date        | Revision                                                                                                                                    | Changes                                                                 |  |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|--|

| 14-Feb-2008 | 1                                                                                                                                           | Initial release                                                         |  |

| 19-Feb-2008 | 2                                                                                                                                           | Updated: Figure 1 on page 1, Figure 3 on page 4                         |  |

| 21-Jul-2008 | 3                                                                                                                                           | Added new SO16 package                                                  |  |

| 30-Sep-2008 | 4                                                                                                                                           | Updated Equation 9, Equation 10                                         |  |

| 16-Jan-2009 | 5                                                                                                                                           | Updated Chapter 7.13 on page 27                                         |  |

| 20-Jul-2009 | 6                                                                                                                                           | Updated application paragraph in coverpage and <i>Table 8 on page</i> 8 |  |

| 14-Jun-2010 | 7                                                                                                                                           | Updated Figure 3 on page 4 and Table 3 on page 4                        |  |

| 23-Jul-2013 | 8                                                                                                                                           | Updated <i>Table 8: Controller section</i> .  Minor text changes.       |  |

| 30-Aug-2013 | 9                                                                                                                                           | Modified the footnote in Table 8: Controller section.                   |  |

|             |                                                                                                                                             |                                                                         |  |

| 16-Feb-2017 | Updated <i>Table 5: "Thermal data"</i> , <i>Table 7: "Supply section "</i> and <i>Table 8: "Controller section "</i> .  Minor text changes. |                                                                         |  |

### **IMPORTANT NOTICE - PLEASE READ CAREFULLY**

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2017 STMicroelectronics - All rights reserved